# UNIVERSIDADE FEDERAL DE SANTA CATARINA CENTRO TECNOLÓGICO DE JOINVILLE PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA DE SISTEMAS ELETRÔNICOS

VALDIR PEDRINHO DE TOMIN JUNIOR

# CONVERSOR DE 4 QUADRANTES A CAPACITOR CHAVEADO COM 5 NÍVEIS DE TENSÃO DE SAÍDA

DISSERTAÇÃO DE MESTRADO - DM - PPGESE - 006

| Valdir Pedrinho de Tomin Junior                                                        |

|----------------------------------------------------------------------------------------|

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

| CONVERSOR DE 4 QUADRANTES A CAPACITOR CHAVEADO COM 5 NÍVEIS DE                         |

| TENSÃO DE SAÍDA                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

| Dissertação submetida ao Programa de Pós-                                              |

| Graduação em Engenharia de Sistemas<br>Eletrônicos da Universidade Federal de Santa    |

| Catarina para a obtenção do título de Mestre em<br>Engenharia de Sistemas Eletrônicos. |

| Orientador: Prof. Hugo Rolando Estofanero Larico, Dr.                                  |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

| Joinville                                                                              |

| 2019                                                                                   |

# Ficha de identificação da obra elaborada pelo autor, através do Programa de Geração Automática da Biblioteca Universitária da UFSC.

Tomin Junior, Valdir Pedrinho de Conversor de 4 quadrantes a capacitor chaveado com 5 níveis de tensão de saída / Valdir Pedrinho de Tomin Junior; orientador, Hugo Rolando Estofanero Larico, 2019. 172 p.

Dissertação (mestrado) - Universidade Federal de Santa Catarina, Campus Joinville, Programa de Pós-Graduação em Engenharia de Sistemas Eletrônicos, Joinville, 2019.

Inclui referências.

1. Engenharia de Sistemas Eletrônicos. 2. Conversor multinível. 3. Capacitor chaveado. 4. Conversor de 4 quadrantes. 5. Eletrônica de potência. I. Estofanero Larico, Hugo Rolando. II. Universidade Federal de Santa Catarina. Programa de Pós-Graduação em Engenharia de Sistemas Eletrônicos. III. Título.

#### Valdir Pedrinho de Tomin Junior

# Conversor de 4 Quadrantes a Capacitor Chaveado com 5 Níveis de Tensão de Saída

O presente trabalho em nível de Mestrado foi avaliado e aprovado por banca examinadora composta pelos seguintes membros:

Prof. Alessandro Luiz Batschauer, Dr. Universidade do Estado de Santa Catarina – UDESC

Prof. Joselito Anastácio Heerdt, Dr. Universidade do Estado de Santa Catarina – UDESC

Certificamos que esta é a **versão original e final** do trabalho de conclusão que foi julgado adequado para obtenção do título de Mestre em Engenharia de Sistemas Eletrônicos.

Prof. Alexandro Garro Brito, Dr. Coordenador do Programa

Prof. Hugo Rolando Estofanero Larico, Dr. Orientador

#### **AGRADECIMENTOS**

Agradeço a Deus, pelo dom da vida, pelas minhas capacidades e pelas pessoas em minha vida.

Agradeço ao meu orientador, professor Hugo R. E. Larico, por me conduzir no desenvolvimento deste trabalho, pela paciência e tolerância às minhas "blasfêmias contra a eletrônica de potência", como costuma dizer, pelos conhecimentos passados e por me mostrar uma visão singular sobre a construção do conhecimento, mas acima de tudo, por sua amizade.

Agradeço ao professor Diego Santos Greff, por todas as contribuições e orientações durante o período do meu mestrado, não só nas questões técnicas, mas também compartilhando sua experiência de vida.

Agradeço à CAPES, pelo apoio financeiro para a realização dos meus estudos.

Agradeço aos membros da banca examinadora, professores Alessandro Luiz Batschauer e Joselito Anastácio Heerdt pela contribuição para a melhoria do presente documento.

Agradeço aos meus pais, Valdir Pedrinho de Tomin e Blandina Neves, pela compreensão e apoio.

Agradeço à minha namorada, Larissa Ester Pereira, por sua paciência e por encorajar-me durante o período de finalização desta dissertação.

Agradeço a todos os brasileiros que pagam seus impostos e viabilizam a gratuidade de instituições como a Universidade Federal de Santa Catarina.

"All we have to decide is what to do with the time that is given us." Gandalf in The Fellowship of the Ring, J. R. R. Tolkien (1954) "É melhor estudar uma única equação, mas entendê-la profundamente, do que estudar várias e não ter pleno entendimento de nenhuma." Hugo R. E. Larico (2017)

#### **RESUMO**

Neste trabalho é proposto um conversor multinível composto por um par de células P2 de 3 níveis de tensão, onde cada célula constitui uma perna de uma estrutura monofásica que opera nos 4 quadrantes, no qual emprega-se uma técnica de capacitor chaveado. O conversor é abaixador de tensão e sintetiza até 5 níveis de tensão de saída. As células são constituídas por 3 capacitores que processam energia através da comutação de 6 interruptores. Dois capacitores são comuns a ambas as células, de modo que a topologia seja constituída por 4 capacitores de processamento de energia e 12 interruptores. O conversor proposto apresenta o auto-balanceamento das tensões dos capacitores de processamento de energia, característica vantajosa frente a outras topologias multiníveis que demandam de estratégias de balanceamento das tensões sobre os capacitores relativamente complexas. A frequência da tensão pulsada na entrada do filtro de saída é 4 vezes a frequência de chaveamento, o que reduz o tamanho do filtro de saída; e os esforços de tensão sobre os semicondutores são, em magnitude, metade da tensão de entrada. Os esforços de corrente nos semicondutores são menores que a corrente de carga, embora desiguais. Este trabalho apresenta a análise estática da variante topológica composta por uma única célula P2 de 3 níveis de tensão, identificada como C4Q-CC-3N. Essa análise demonstra que o C4Q-CC-3N possuí uma faixa de operação limitada, o que justifica o estudo da topologia proposta, identificada como C4Q-CC-5N. Os valores médios do C4Q-CC-5N são obtidos utilizando-se a técnica de espaço de estados. As ondulações de tensão nos capacitores e de corrente nos indutores, bem como os esforços de corrente nos semicondutores e capacitores são obtidos analisando-se as formas de onda sobre esses componentes. Além disso, é obtido um modelo de pequenos sinais de segunda ordem, o qual descreve a dinâmica do sistema. O equacionamento é adaptado para a operação como inversor de tensão e a teoria é verificada, quantitativamente, comparando-se resultados de simulações com valores teóricos previstos pelas equações desenvolvidas para ambos os modos de operação: conversor cc-cc e inversor de tensão. Por fim, são apresentados resultados experimentais obtidos com um protótipo de 115 W operando como inversor, com tensão de entrada de 48 V, tensão eficaz de saída de 110 V / 50 Hz e frequência de chaveamento de 10 kHz. Os resultados validam o princípio de funcionamento proposto.

**Palavras-chave**: Conversor multinível, Capacitor chaveado, Conversor de 4 quadrantes, Inversor.

#### **ABSTRACT**

This work proposes a multilevel converter composed of a pair of 3-level P2 cells, where each cell constitutes a leg of a 4-guadrants single-phase structure, using a switched capacitor technique. The converter is a step-down converter that synthesizes up to 5 output voltage levels. The cells consist of 3 power processing capacitors switched by 6 power switches. Two capacitors are shared by both cells. Thus, the topology consists of 4 power processing capacitors and 12 power switches. The proposed converter presents a self voltage balancing on the power processing capacitors, an advantageous feature compared to other multilevel topologies that require relatively complex strategies for voltage balancing. The frequency of the pulsed voltage at the output filter input is four times the switching frequency, which reduces the size of the output filter; and the current stresses on semiconductors are, in magnitude, half of the input voltage. The current stresses on semiconductors are lower than the load current, although unequal. This work presents the static analysis of the topological variant composed by a single 3-level P2 cell, identified as the half-bridge converter. This analysis shows that the half-bridge converter has a limited operating range, justifying the study of the proposed topology, identified as the full-bridge converter. The mean values of the fullbridge are obtained using the state-space technique. The voltage ripples on capacitors and current ripples on inductors as well as current stresses on semiconductors and capacitors are obtained analyzing the waveforms on these components. Furthermore, a second-order small-signals model is obtained, which describes the system dynamics. The equations are adapted for operation as a voltage inverter, and the theory is verified, quantitatively, comparing simulation data with the theoretical values predicted by the developed equations for both operations modes: dc-dc converter and voltage inverter. Finally, is presented the experimental data obtained from a prototype of 115 W operating as a voltage inverter with an input voltage of 48 V, RMS output voltage of 110 V / 50 Hz, and switching frequency of 10 kHz. The experimental data validates the principle of operation.

**Keywords**: Multilevel converter, Switched capacitor, 4-guadrant converter, Inverter.

## LISTA DE FIGURAS

| Figura 2.1 – Célula básica de capacitor chaveado                                                                                           | 40 |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 2.2 – Sub-circuitos equivalentes do SCC da Fig. 2.1                                                                                 | 40 |

| Figura 2.3 - Circuito genérico de carga / descarga do capacitor                                                                            | 40 |

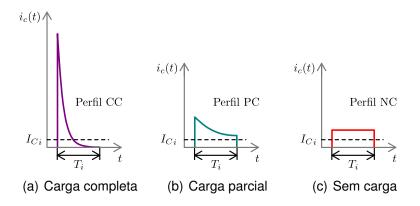

| Figura 2.4 – Possíveis perfis de carga do capacitor $C_i$ da Fig. 2.4                                                                      | 41 |

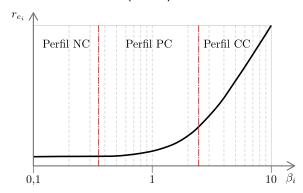

| Figura 2.5 - Comportamento da resistência equivalente em função do parâme-                                                                 |    |

| tro $\beta_i$ – Adaptado de Ben-Yaakov (2012)                                                                                              | 42 |

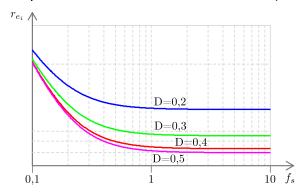

| Figura 2.6 – Dependência da resistência equivalente em função da frequência                                                                |    |

| normalizada – Adaptado de Ben-Yaakov e Evzelman (2009)                                                                                     | 42 |

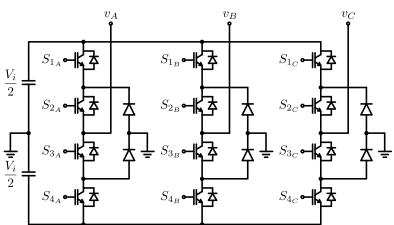

| Figura 2.7 - Conversor NPC trifásico de 3 níveis                                                                                           | 44 |

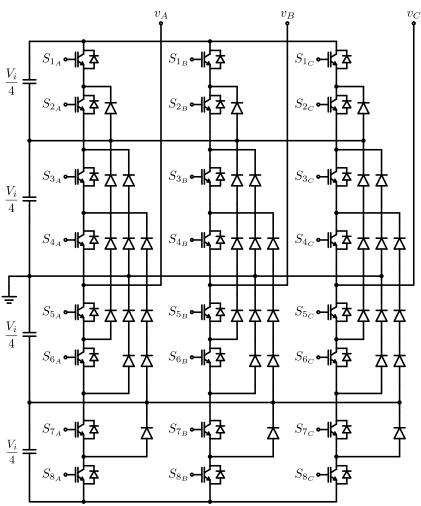

| Figura 2.8 - Conversor NPC trifásico de 5 níveis                                                                                           | 46 |

| Figura 2.9 - Conversor NPC de 5 níveis trifásico sem ligação série de diodos .                                                             | 47 |

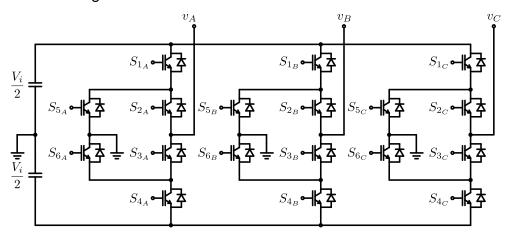

| Figura 2.10 – Conversor ANPC trifásico de 3 níveis                                                                                         | 48 |

| Figura 2.11 – Conversor TNPC trifásico de 3 níveis                                                                                         | 48 |

| Figura 2.12 – Conversor FC trifásico de 3 níveis                                                                                           | 49 |

| Figura 2.13 – Conversor FC trifásico de 5 níveis                                                                                           | 50 |

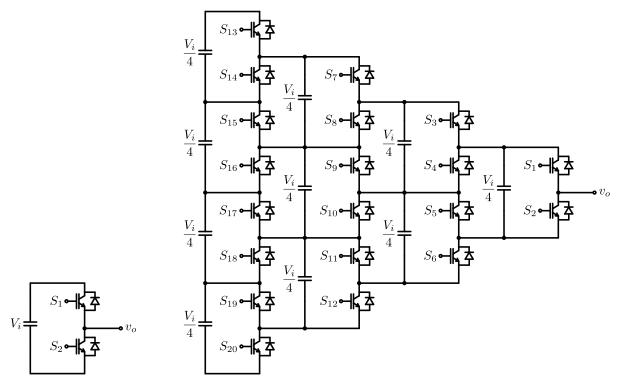

| Figura 2.14 – Topologia multinível generalizada com auto-balanço de tensões .                                                              | 52 |

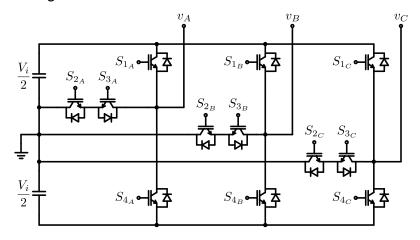

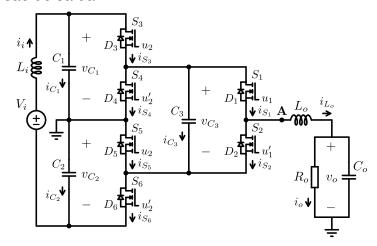

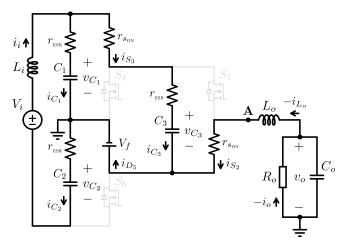

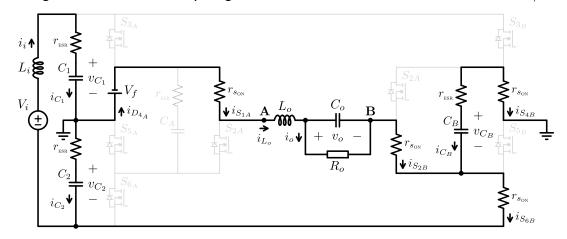

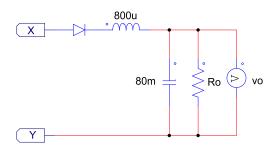

| Figura 3.1 - Conversor de 4 de quadrantes a capacitor chaveado com 3 níveis                                                                |    |

| de tensão de saída                                                                                                                         | 55 |

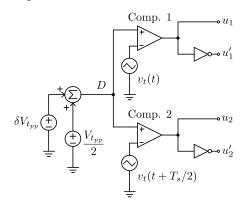

| Figura 3.2 - Circuito analógico modulador dos sinais de comando do C4Q-CC-3N                                                               | 56 |

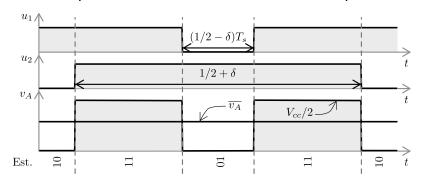

| Figura 3.3 — Principais formas de onda do C4Q-CC-3N para $0 \leqslant \delta \leqslant 1/2$                                                | 58 |

| Figura 3.4 — Estado topológico 11 do C4Q-CC-3N com $0 \leqslant \delta \leqslant 1/2 \ldots$                                               | 59 |

| Figura 3.5 — Estado topológico 01 do C4Q-CC-3N com $0 \leqslant \delta \leqslant 1/2 \ldots$                                               | 60 |

| Figura 3.6 — Estado topológico 10 do C4Q-CC-3N com $0 \leqslant \delta \leqslant 1/2 \ldots$                                               | 60 |

| Figura 3.7 — Principais formas de onda do C4Q-CC-3N para $-1/2 \leqslant \delta \leqslant 0$ .                                             | 62 |

| Figura 3.8 — Estado topológico 00 do C4Q-CC-3N com $-1/2 \leqslant \delta \leqslant 0 \ldots$                                              | 63 |

| Figura 3.9 — Estado topológico 10 do C4Q-CC-3N com $-1/2 \leqslant \delta \leqslant 0 \ldots$                                              | 63 |

| Figura 3.10 – Estado topológico 01 do C4Q-CC-3N com $-1/2 \leqslant \delta \leqslant 0$                                                    | 64 |

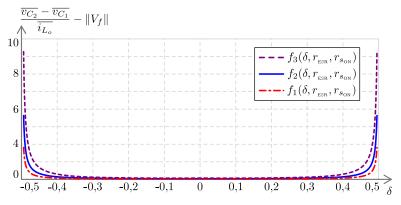

| Figura 3.11 — Diferença de tensão entre os capacitores em função de $\delta, r_{s_{\mathrm{on}}}$ e $r_{\scriptscriptstyle{\mathrm{ESR}}}$ | 66 |

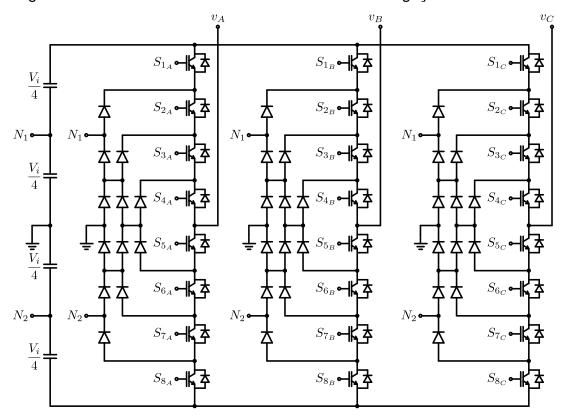

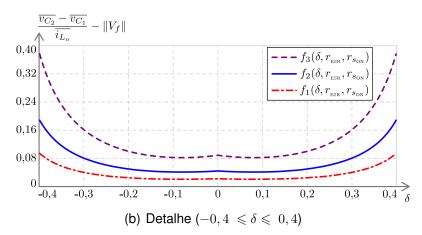

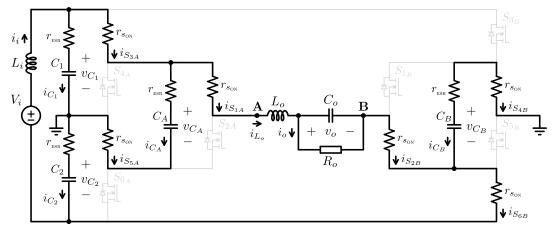

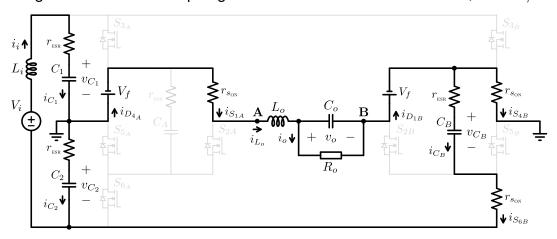

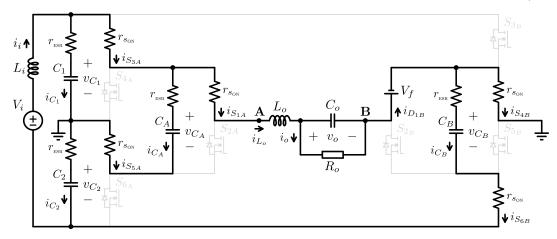

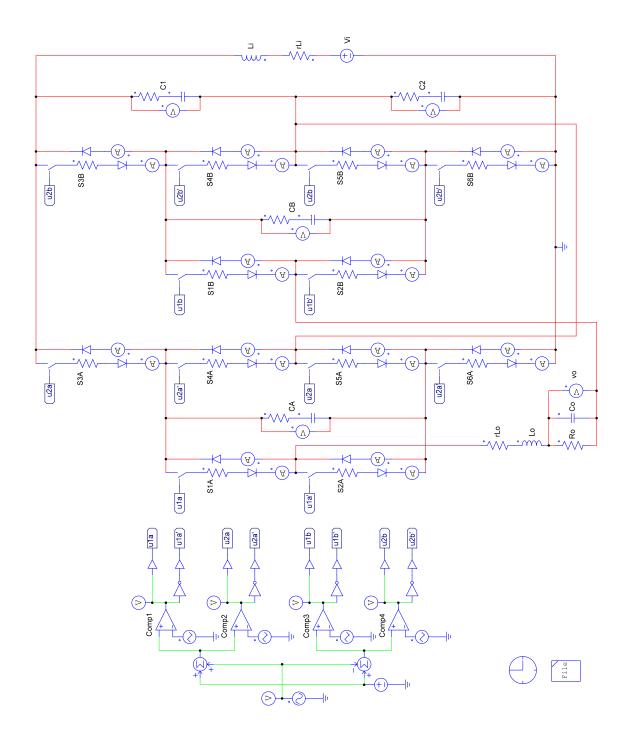

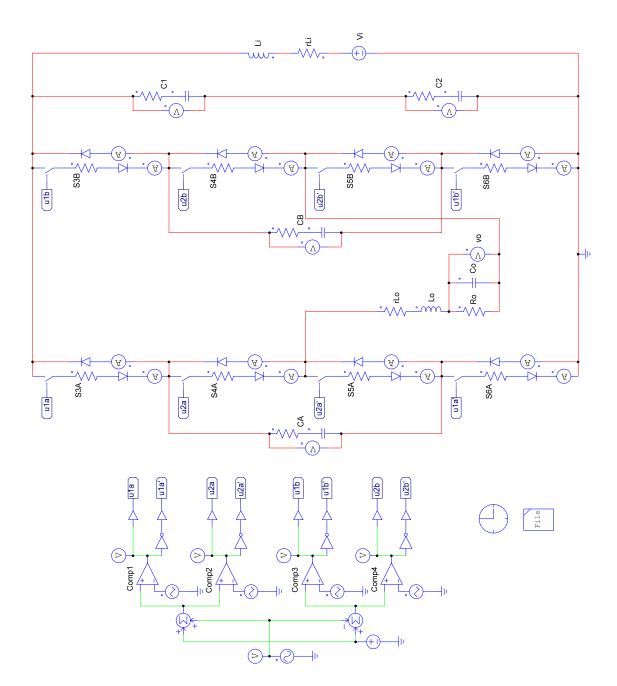

| Figura 4.1 - Conversor de 4 de quadrantes a capacitor chaveado com 5 níveis                                                                |    |

| de tensão de saída                                                                                                                         | 67 |

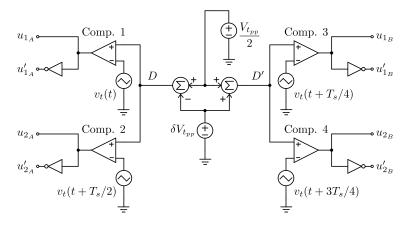

| Figura 4.2 - Circuito analógico modulador dos sinais de comando do C4Q-CC-5N                                                               | 67 |

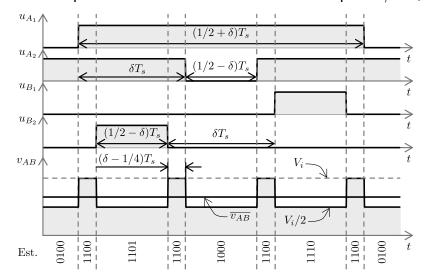

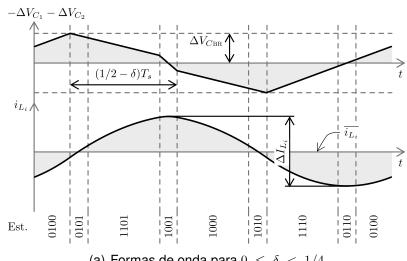

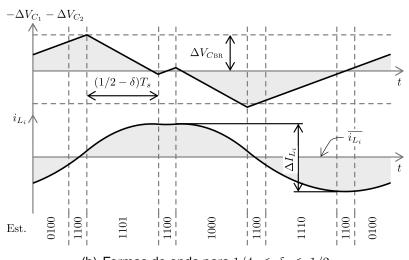

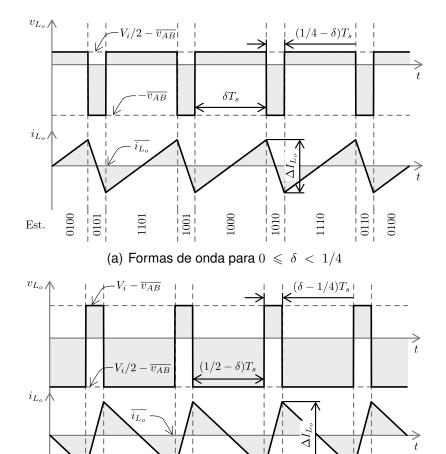

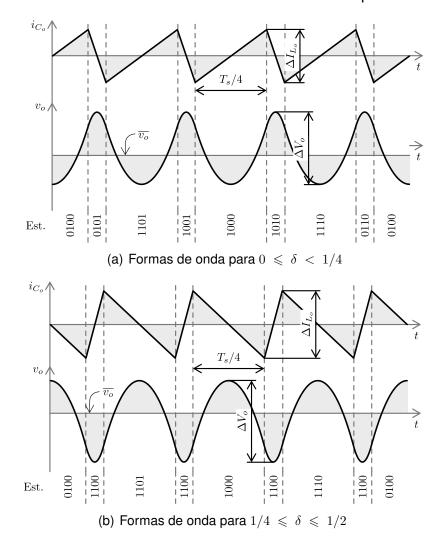

| Figura 4.3 – Principais formas de onda do C4Q-CC-5N para $1/4 \leqslant \delta \leqslant 1/2$ .                                            | 70 |

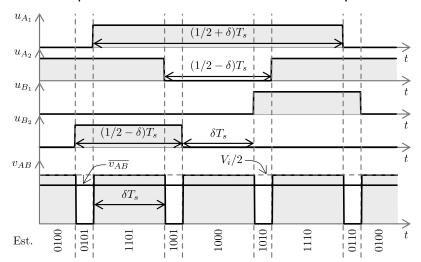

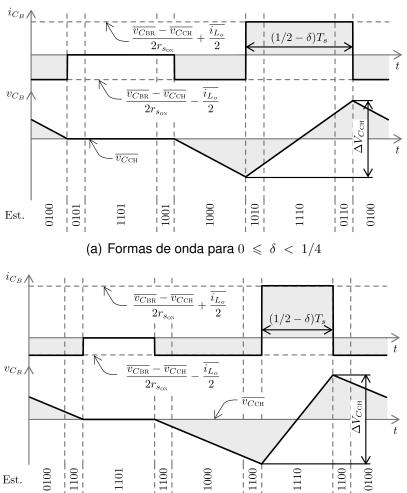

| Figura 4.4 - Principais formas de onda do C4Q-CC-5N para $0 \leqslant \delta < 1/4$                                                        | 71 |

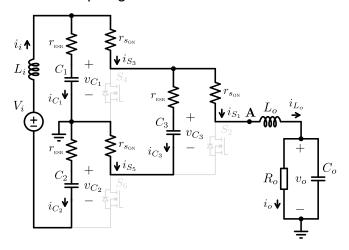

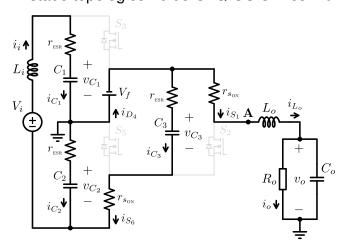

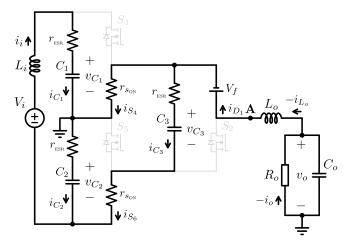

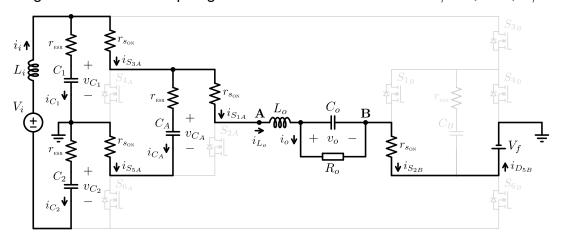

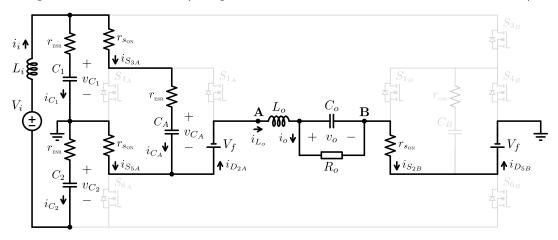

| Figura 4.5 — Estado topológico 1100 do C4Q-CC-5N com $1/4 \leqslant \delta \leqslant 1/2$                                                  | 74 |

| Figura 4.6 — Estado topológico 0100 do C4Q-CC-5N com $1/4 \leqslant \delta \leqslant 1/2$                                                  | 74 |

| Figura 4.7 — Estado topológico 1101 do C4Q-CC-5N com $1/4 \leqslant \delta \leqslant 1/2$                                                  | 75 |

| Figura 4.8 — Estado topológico 1000 do C4Q-CC-5N com $1/4 \leqslant \delta \leqslant 1/2$                                                  | 76 |

| Figura 4.9 — Estado topológico 1110 do C4Q-CC-5N com $1/4 \leqslant \delta \leqslant 1/2$ 77 |

|----------------------------------------------------------------------------------------------|

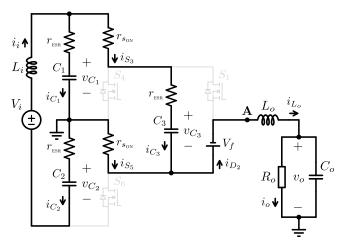

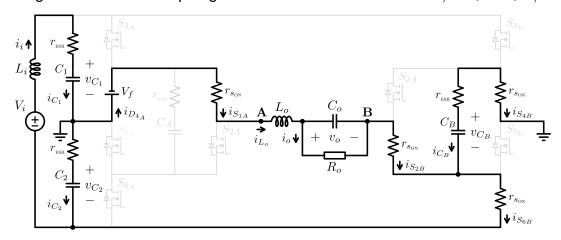

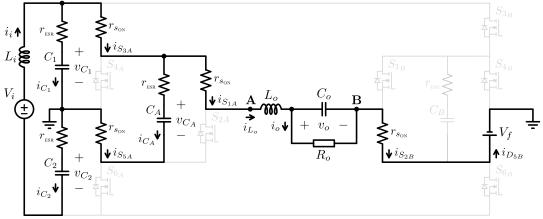

| Figura 4.10 — Estado topológico 0100 do C4Q-CC-5N com $0 \leqslant \delta < 1/4 \ldots$ 78   |

| Figura 4.11 — Estado topológico 0101 do C4Q-CC-5N com $0 \leqslant \delta < 1/4 \ldots$ 78   |

| Figura 4.12 – Estado topológico 1101 do C4Q-CC-5N com $0 \leqslant \delta < 1/4 \ldots$ 79   |

| Figura 4.13 – Estado topológico 1001 do C4Q-CC-5N com $0 \leqslant \delta < 1/4$ 80          |

| Figura 4.14 – Estado topológico 1000 do C4Q-CC-5N com $0 \leqslant \delta < 1/4$ 80          |

| Figura 4.15 – Estado topológico 1010 do C4Q-CC-5N com $0 \leqslant \delta < 1/4 \ldots$ 81   |

| Figura 4.16 — Estado topológico 1110 do C4Q-CC-5N com $0 \leqslant \delta < 1/4$ 82          |

| Figura 4.17 — Estado topológico 0110 do C4Q-CC-5N com $0 \leqslant \delta < 1/4$ 83          |

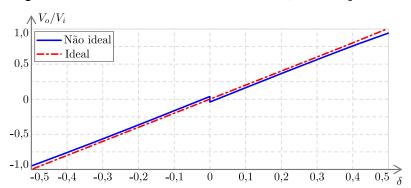

| Figura 4.18 – Tensão média de saída $V_o$ em função de $\delta$                              |

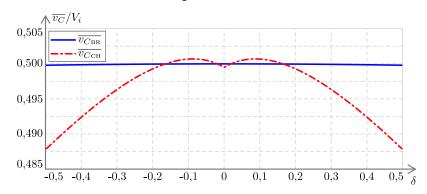

| Figura 4.19 – Tensão média nos capacitores de barramento $V_{CBR}$ e nos capacito-           |

| res chaveados $V_{C\mathrm{CH}}$ em função $\delta$                                          |

| Figura 4.20 – Formas de onda de corrente e tensão nos capacitores chaveados 87               |

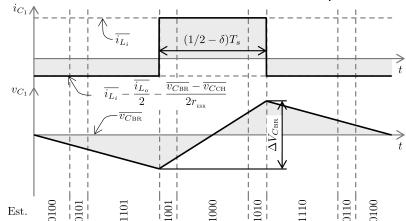

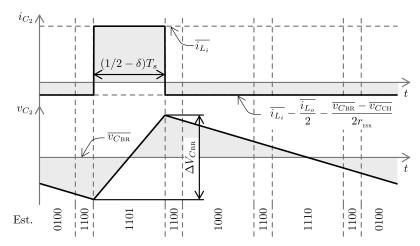

| Figura 4.21 – Formas de onda de corrente e tensão nos capacitores de barramento 88           |

| Figura 4.22 – Formas de onda da soma das ondulações de tensão nos capacito-                  |

| res $C_1$ e $C_2$ e corrente no indutor de entrada $L_i$                                     |

| Figura 4.23 – Formas de onda de tensão e corrente no indutor de saída $L_o \ \dots \ 90$     |

| Figura 4.24 — Formas de onda de corrente e tensão no capacitor de saída $C_o$ 91             |

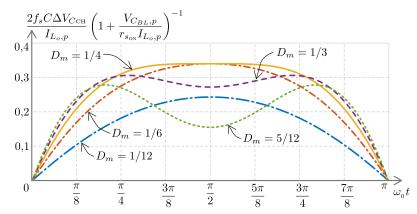

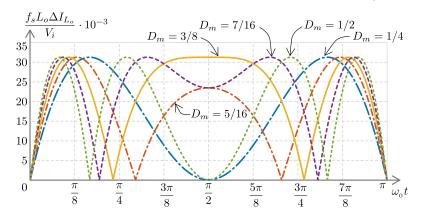

| Figura 5.1 – Ondulação $\Delta V_{C\mathrm{CH}}$ normalizada nos capacitores chaveados para  |

| um período da onda sinusoidal da tensão de saída 105                                         |

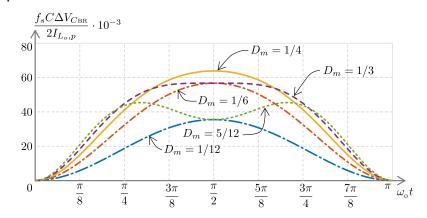

| Figura 5.2 – Ondulação $\Delta V_{C_{ m BR}}$ normalizada nos capacitores de barramento      |

| para um período da onda sinusoidal da tensão de saída 105                                    |

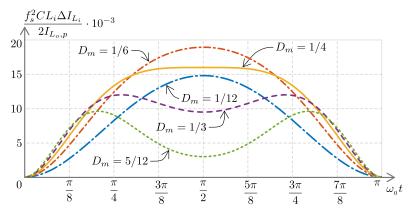

| Figura 5.3 - Ondulação $\Delta I_{L_i}$ normalizada no indutor de entrada para um pe-        |

| ríodo da onda sinusoidal da tensão de saída                                                  |

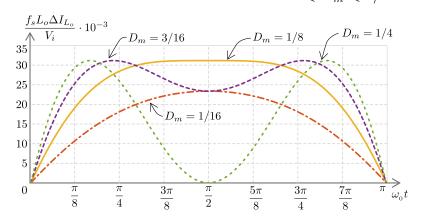

| Figura 5.4 — Ondulação $\Delta I_{L_o}$ normalizada no indutor de saída para um período      |

| da onda sinusoidal da tensão de saída com $0 \leqslant D_m \leqslant 1/4$ 107                |

| Figura 5.5 – Ondulação $\Delta I_{L_o}$ normalizada no indutor de saída para um período      |

| da onda sinusoidal da tensão de saída com $0 \leqslant D_m \leqslant 1/2$ 109                |

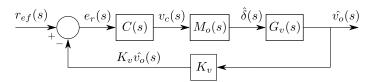

| Figura 6.1 – Diagrama de blocos da malha de controle                                         |

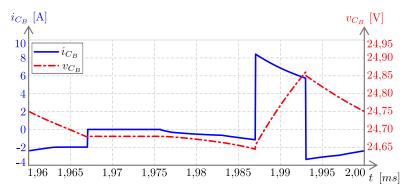

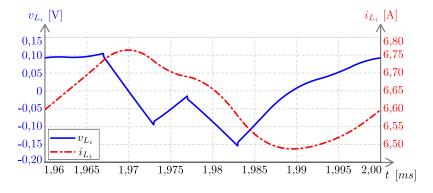

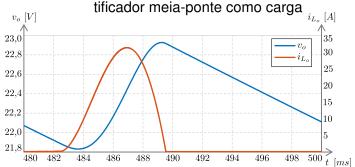

| Figura 6.2 - Resultados de simulação - Formas de onda de corrente e tensão                   |

| no capacitor $C_B$ em regime permanente e malha aberta                                       |

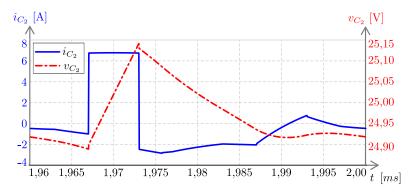

| Figura 6.3 - Resultados de simulação - Formas de onda de corrente e tensão                   |

| no capacitor $C_2$ em regime permanente e malha aberta 117                                   |

| Figura 6.4 - Resultados de simulação - Formas de onda de tensão e corrente                   |

| no indutor $L_i$ em regime permanente e malha aberta                                         |

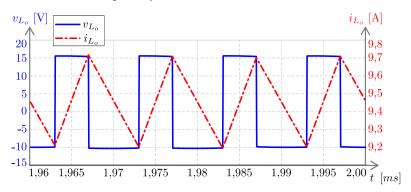

| Figura 6.5 - Resultados de simulação - Formas de onda de tensão e corrente                   |

| no indutor $L_o$ em regime permanente e malha aberta 118                                     |

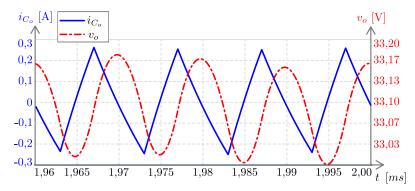

| Figura 6.6 - Resultados de simulação - Formas de onda de corrente e tensão                   |

| no capacitor $C_o$ em regime permanente e malha aberta                                       |

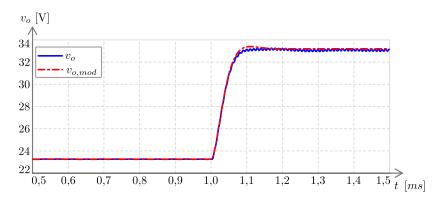

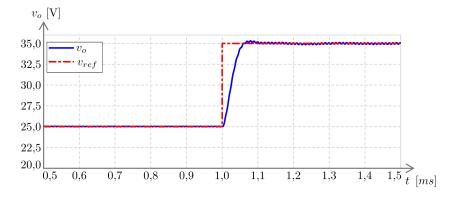

| Figura 6.7 -  | Resultados de simulação - Comparativo da resposta da tensão                          |     |

|---------------|--------------------------------------------------------------------------------------|-----|

|               | de saída $v_o(t)$ do modelo de pequenos sinais com a resposta do                     |     |

|               | circuito simulado em malha aberta para um degrau na razão cíclica                    |     |

|               | de $\delta=0,25$ para $\delta=0,35$                                                  | 120 |

| Figura 6.8 -  | Resultados de simulação — Resposta da tensão de saída $v_o(t)$ para                  |     |

|               | um degrau na referência de $r_{ef}(t)$ = 25 V para $r_{ef}(t)$ = 35 V com o          |     |

|               | sistema em malha fechada                                                             | 120 |

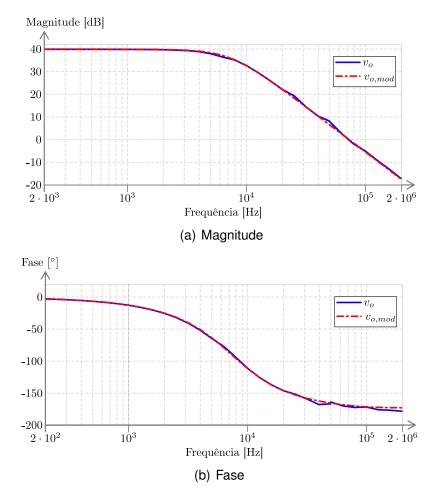

| Figura 6.9 -  | Resultados de simulação – Diagramas de Bode da tensão de saída                       |     |

|               | $v_o$ para frequências de 200 Hz a 200 kHz. Resposta do circuito                     |     |

|               | simulado em malha aberta contraposta a resposta do modelo de                         |     |

|               | pequenos sinais                                                                      | 121 |

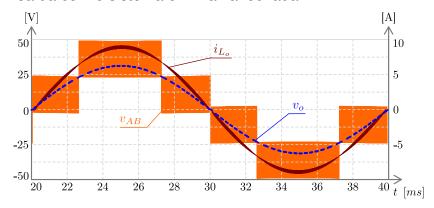

| Figura 6.10 - | Resultados de simulação — Tensão $v_{AB}$ na entrada do filtro de saída              |     |

|               | e tensão de saída $v_o$ para um período da onda sinusoidal da tensão                 |     |

|               |                                                                                      | 122 |

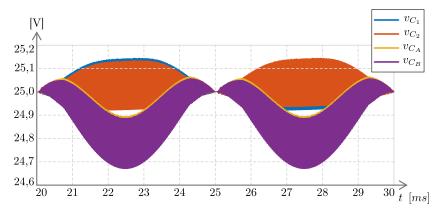

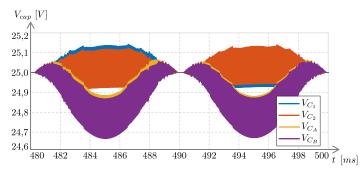

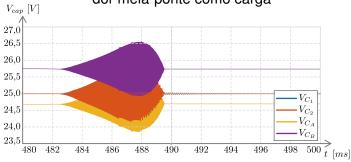

| Figura 6.11 – | Resultados de simulação - Tensão nos capacitores para um pe-                         |     |

|               | ríodo da onda sinusoidal da tensão de saída com o sistema em                         |     |

|               | malha fechada                                                                        | 122 |

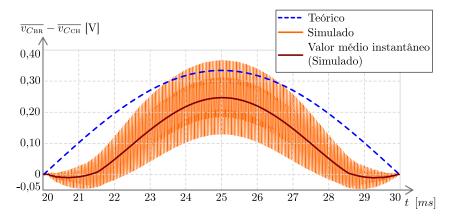

| Figura 6.12 – | Resultados de simulação – Diferença de tensão entre os capacito-                     |     |

|               | res para um período da onda sinusoidal da tensão de saída com o                      |     |

|               | sistema em malha fechada                                                             | 122 |

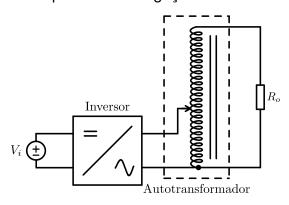

|               | Esquemático de ligação com autotransformador                                         | 125 |

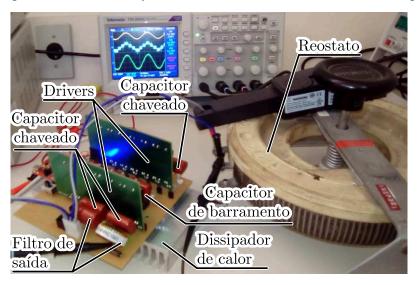

|               | Protótipo – Teste com um reostato como carga                                         | 125 |

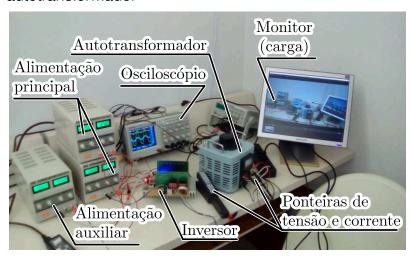

| Figura 6.15 – | Protótipo – Teste com um monitor como carga, acoplado à saída                        |     |

|               | do autotransformador                                                                 | 126 |

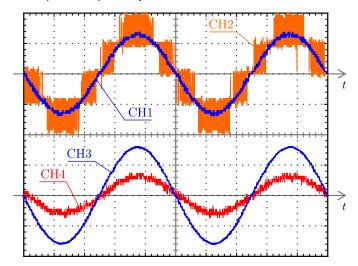

| •             | Resultados experimentais – Principais formas de onda do conver-                      |     |

|               | sor proposto — CH1 - Tensão de saída ( $25\ V/{\rm div}$ ); CH2 - Tensão $AB$        |     |

|               | (25 $V/{\rm div}$ ); CH3 - Tensão na saída do autotransformador (100 $V/{\rm div}$ ) |     |

|               | CH4 - Corrente de saída (2 $A$ /div); tempo: 4 $ms$ /div                             | 126 |

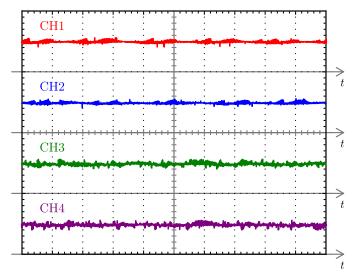

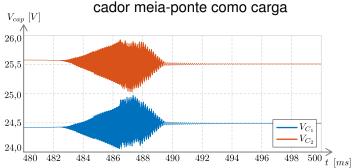

| Figura 6.17 – | Resultados experimentais – Tensões nos capacitores – CH1 - Ten-                      |     |

|               | são no capacitor $C_1$ (25 V/div); CH2 - Tensão no capacitor $C_2$ (25 V/-           |     |

|               | div); CH3 - Tensão no capacitor $C_A$ (25 V/div); CH4 - Tensão no                    |     |

|               | capacitor $C_B$ (25 V/div); tempo: 4 ms/div                                          | 127 |

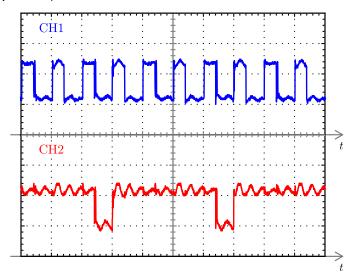

| _             | Resultados experimentais — Tensão $v_{AB}$ e tensão sobre um inter-                  |     |

|               | ruptor – CH1 - Tensão $AB$ (20 V/div); CH2 - Tensão no interruptor                   |     |

|               | $S_{5_B}$ (20 V/div); tempo: 25 $\mu$ s/div                                          | 127 |

## **LISTA DE TABELAS**

| Tabela 2.1 - | Tensão de saída por perna para os diferentes estados de comuta-                            |     |

|--------------|--------------------------------------------------------------------------------------------|-----|

|              | ção do NPC de 3 níveis                                                                     | 45  |

| Tabela 2.2 - | Tensão de saída por perna para os diferentes estados de comuta-                            |     |

|              | ção do ANPC de 3 níveis                                                                    | 48  |

| Tabela 2.3 - | Tensão de saída por perna para os diferentes estados de comuta-                            |     |

|              | ção do TNPC de 3 níveis                                                                    | 49  |

| Tabela 2.4 - | Tensão de saída por perna para os diferentes estados de comuta-                            |     |

|              | ção do FC de 3 níveis                                                                      | 50  |

| Tabela 2.5 - | Número de componentes, por perna, para as topologias NPC, FC                               |     |

|              | e P2 para $n$ níveis de tensão de fase                                                     | 52  |

| Tabela 3.1 - | Tensão na entrada do filtro de saída para $0 \leqslant \delta \leqslant 1/2 \ldots \ldots$ | 58  |

| Tabela 3.2 - | Tensão na entrada do filtro de saída para $-1/2 \leqslant \delta \leqslant 0 \ldots$       | 62  |

| Tabela 4.1 - | Sequências de chaveamento por região de operação do conversor                              | 69  |

| Tabela 4.2 - | Tensão $v_{AB}$ na entrada do filtro de saída para $1/4 \leqslant \delta \leqslant 1/2$    | 70  |

| Tabela 4.3 - | Tensão $v_{AB}$ na entrada do filtro de saída para $0 \leqslant \delta < 1/4$              | 71  |

| Tabela 4.4 - | Esforços nos semicondutores — Perna $A$ — para $0 \leqslant \delta \leqslant 1/2$          | 93  |

| Tabela 4.5 - | Esforços nos semicondutores — Perna $B$ — para $0 \leqslant \delta \leqslant 1/2$          | 93  |

| Tabela 5.1 - | Esforços nos semicondutores – Conversor operando como inversor                             | 112 |

| Tabela 6.1 - | Especificações de projeto do circuito simulado                                             | 113 |

| Tabela 6.2 - | Componentes de potência do circuito simulado                                               | 115 |

| Tabela 6.3 - | Resultados de simulação – Valores médios, ondulações e esforços                            |     |

|              | de corrente nos componentes para operação como conversor cc-                               |     |

|              | cc em regime permanente e malha aberta                                                     | 119 |

| Tabela 6.4 - | Resultados de simulação – Valores médios, ondulações e esforços                            |     |

|              | de corrente nos componentes para operação como inversor em                                 |     |

|              | regime permanente e malha aberta                                                           | 123 |

| Tabela 6.5 - | Especificações de projeto do protótipo                                                     | 124 |

| Tabela 6.6 - | Componentes de potência do protótipo                                                       | 125 |

## LISTA DE ABREVIATURAS E SIGLAS

| CC         | Corrente contínua                                              | 33  |

|------------|----------------------------------------------------------------|-----|

| ca         | Corrente alternada                                             | 33  |

| MOSFET     | Metal-oxide-semiconductor field effect transistor              | 33  |

| IGBT       | Insulated gate bipolar transistor                              | 33  |

| GTO        | Gate turn-off thyristor                                        | 33  |

| UPS        | Uninterruptible power supplies                                 | 34  |

| THD        | Total harmonic distortion                                      | 34  |

| C4Q-CC-5N  | Conversor de 4 de quadrantes a capacitor chaveado com 5 níveis |     |

|            | de tensão de saída                                             | 36  |

| C4Q-CC-3N  | Conversor de 4 de quadrantes a capacitor chaveado com 3 níveis |     |

|            | de tensão de saída                                             | 36  |

| cc-cc      | Conversão de corrente contínua para corrente contínua          | 36  |

| cc-ca      | Conversão de corrente contínua para corrente alternada         | 36  |

| SCC        | Switched capacitor converter                                   | 39  |

| $E^2$ PROM | Electrically-erasable programmable read-only memory            | 39  |

| CC         | Complete charge                                                | 41  |

| PC         | Partial charge                                                 | 41  |

| NC         | No charge                                                      | 41  |

| EMI        | Electromagnetic interference                                   | 44  |

| NPC        | Neutral Point Clamped                                          | 44  |

| FACTS      | Flexible alternate current transmission systems                | 45  |

| PWM        | Pulse width modulation                                         | 45  |

| ANPC       | Active Neutral Point Clamped                                   | 47  |

| NPP        | Neutral point piloted                                          | 47  |

| FC         | Flying Capacitor                                               | 49  |

| CCM        | Continuous conduction mode                                     | 57  |

| SISO       | Single input single output                                     | 68  |

| RP         | Regime permanente                                              | 113 |

| PID        | Controlador proporcional integrador derivativo                 | 116 |

# LISTA DE SÍMBOLOS

| $r_{s_{ m on}}$                       | Resistencia de condução do interruptor                             | 40 |

|---------------------------------------|--------------------------------------------------------------------|----|

| $r_{\scriptscriptstyle \mathrm{ESR}}$ | Resistência série-equivalente do capacitor                         | 40 |

| $T_s$                                 | Período de comutação                                               | 41 |

| D                                     | Razão cíclica                                                      | 42 |

| $S_x$                                 | Interruptor $x$                                                    | 44 |

| $v_o$                                 | Tensão instantânea de saída                                        | 44 |

| $V_{i}$                               | Tensão de entrada (cc)                                             | 44 |

| $V_{i}$                               | Tensão no barramento de entrada (DC)                               | 55 |

| $C_x$                                 | Capacitor $x$                                                      | 55 |

| $L_x$                                 | Indutor $x$                                                        | 55 |

| $S_x$                                 | Interruptor $x$                                                    | 55 |

| $R_o$                                 | Resistência de carga                                               | 55 |

| $i_{L_i}$                             | Corrente instantânea de entrada                                    | 55 |

| $i_{L_o}$                             | Corrente instantânea de saída                                      | 55 |

| $i_{C_x}$                             | Corrente instantânea no capacitor $x$                              | 55 |

| $i_{S_x}$                             | Corrente instantânea no interruptor $x$                            | 55 |

| $v_{C_x}$                             | Tensão instantânea no capacitor $x$                                | 55 |

| $v_o$                                 | Tensão instantânea de saída                                        | 55 |

| $i_o$                                 | Corrente na carga                                                  | 55 |

| $f_s$                                 | Frequência de comutação                                            | 56 |

| $v_t(t)$                              | Tensão triangular das portadoras triangulares do modulador         | 56 |

| $V_{t_{pp}}$                          | Amplitude de pico a pico da tensão das portadoras triangulares do  |    |

|                                       | modulador                                                          | 56 |

| $P_i$                                 | Potência de entrada                                                | 57 |

| $P_o$                                 | Potência de saída                                                  | 57 |

| $\overline{v_A}$                      | Tensão média instantânea na entrada do filtro de saída (C4Q-CC-3N) | 57 |

| $\Delta t$                            | Intervalo de tempo                                                 | 57 |

| $\overline{v_o}$                      | Tensão média instantânea na carga                                  | 58 |

| $\overline{i_{L_i}}$                  | Corrente média instantânea de entrada                              | 58 |

| $\overline{i_{L_o}}$                  | Corrente média instantânea de saída                                | 58 |

| $V_f$                                 | Queda de tensão no diodo anti-paralelo do interruptor              | 60 |

| $\overline{i_{C_x}}$                  | Corrente média instantânea no capacitor $x$                        | 61 |

| $\overline{v_{C_x}}$                  | Tensão média instantânea no capacitor $x$                          | 61 |

| $\ V_f\ $                             | Queda de tensão $V_f$ normalizada por $\overline{i_{L_o}}$         | 61 |

| $\overline{v_{AB}}$                   | Tensão média instantânea na entrada do filtro de saída             | 69 |

| $[\mathbf{x}]$                        | Vetor das variáveis de estado                                      | 72 |

| [ <b>v</b> ]                          | Vetor das variáveis de saída                                       | 72 |

| $[\mathbf{A}]$                                     | Matriz das variáveis de estado                                                  | 72 |

|----------------------------------------------------|---------------------------------------------------------------------------------|----|

| [B]                                                | Matriz de entrada ou de perturbações                                            | 72 |

| $[\mathbf{C}]$                                     | Matriz de saída                                                                 | 72 |

| $v_{C_{\mathrm{BR}}}$                              | Tensão instantânea nos capacitores de barramento                                | 73 |

| $v_{C\mathrm{CH}}$                                 | Tensão instantânea nos capacitores chaveados                                    | 73 |

| $\overline{v_{C{\scriptscriptstyle \mathrm{BR}}}}$ | Tensão média instantânea nos capacitores de barramento                          | 73 |

| $\overline{v_{C{\scriptscriptstyle \mathrm{CH}}}}$ | Tensão média instantânea nos capacitores chaveados                              | 73 |

| $\overline{v_{C_x}}$                               | Tensão média instantânea no capacitor $C_x$                                     | 73 |

| C                                                  | Capacitância padronizada para os capacitores $C_1,C_2,C_A$ e $C_B$              | 73 |

| $x_k$                                              | Variável de estado                                                              | 83 |

| $\overline{x_k}$                                   | Valor médio instantâneo da variável de estado $x_k$                             | 83 |

| $\lceil \overline{\mathbf{A}}  ceil$               | Matriz média instantânea das variáveis de estado                                | 83 |

| $[\overline{\mathbf{B}}]$                          | Matriz média instantânea de entrada                                             | 83 |

| $[C_k]$                                            | Matriz de saída para a variável de estado $x_k$                                 | 83 |

| $V_o$                                              | Tensão média de saída                                                           | 84 |

| $I_o$                                              | Corrente média de saída                                                         | 84 |

| $I_{L_o}$                                          | Corrente média no indutor $L_o$ , mesmo que corrente média de saída             | 84 |

| $I_i$                                              | Corrente média de entrada                                                       | 84 |

| $I_{L_i}$                                          | Corrente média no indutor $L_i$ , mesmo que corrente média de entrada           | 84 |

| $V_{C^{\mathrm{BR}}}$                              | Tensão média nos capacitores de barramento                                      | 84 |

| $V_{C{\scriptscriptstyle \mathrm{CH}}}$            | Tensão média nos capacitores chaveados                                          | 84 |

| $\Delta V_{C{\scriptscriptstyle \mathrm{CH}}}$     | Ondulação de tensão nos capacitores chaveados                                   | 86 |

| $i_{C\mathrm{CH}}$                                 | Corrente instantânea nos capacitores chaveados                                  | 87 |

| $\overline{i_{C{ m CH}}}_{,{ m RMS}}$              | Corrente eficaz instantânea nos capacitores chaveados                           | 87 |

| $\Delta V_{C^{\mathrm{BR}}}$                       | Ondulação de tensão nos capacitores de barramento                               | 88 |

| $i_{C^{\mathrm{BR}}}$                              | Corrente instantânea nos capacitores de barramento                              | 88 |

| $\overline{i_{C^{\mathrm{BR}},\mathrm{RMS}}}$      | Corrente eficaz instantânea nos capacitores de barramento                       | 88 |

| $\Delta I_{L_i}$                                   | Ondulação de corrente de entrada                                                | 89 |

| $\Delta I_{L_o}$                                   | Ondulação de corrente de saída                                                  | 90 |

| $\Delta V_o$                                       | Ondulação de tesão de saída                                                     | 91 |

| $\overline{i_{C_o}}_{,\mathrm{RMS}}$               | Corrente eficaz no capacitor de saída                                           | 92 |

| $V_{r_x}$                                          | Máxima tensão revesa sobre qualquer semicondutor $x$                            | 92 |

| $\overline{i_x}$                                   | Corrente média instantânea no semicondutor $x$                                  | 92 |

| $\overline{i_x}_{, \mathrm{RMS}}$                  | Corrente eficaz instantânea no semicondutor $x \ldots \ldots \ldots$            | 92 |

| $[\overline{\mathbf{x}}]$                          | Vetor dos valores médio instantâneo das variáveis de estado                     | 97 |

| $\hat{i_{L_o}}(t)$                                 | Pequena perturbação na corrente média instantânea de saída $\overline{i_{L_o}}$ |    |

|                                                    | em torno do ponto quiescente $I_{L_o}$                                          | 98 |

| $\hat{v_o}(t)$                                     | Pequena perturbação na tensão média instantânea de saída $\overline{v_o}$ em    |    |

|                                                    | torno do ponto quiescente $V_o$                                                 | 98 |

| $\hat{\delta}(t)$                                                 | Pequena perturbação na perturbação média instantânea $\overline{\delta}$ sobre a |     |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|

|                                                                   | razão cíclica $D$ em torno do ponto quiescente $\delta$                          | 98  |

| $[\mathbf{\hat{x}}]$                                              | Vetor das perturbações sobre variáveis de estado                                 | 98  |

| $[\mathbf{\hat{y}}]$                                              | Vetor das perturbações sobre variáveis de saída linearizadas                     | 98  |

| $[ {f A}  ]$                                                      | Matriz média instantânea das variáveis de estado linearizada                     | 98  |

| [ <b>B</b> ]                                                      | Matriz média instantânea de entrada linearizada                                  | 98  |

| [I]                                                               | Matriz identidade                                                                | 98  |

| s                                                                 | Variável de Laplace (domínio da frequência)                                      | 98  |

| $G_v(s)$                                                          | Função de transferência de pequenos sinais, de uma perturbação                   |     |

|                                                                   | na perturbação da razão cíclica para uma perturbação na tensão                   |     |

|                                                                   | de saída                                                                         | 99  |

| $D_m$                                                             | Índice de modulação                                                              | 103 |

| $\omega_{ m o}$                                                   | Velocidade angular ou pulsação da onda de tensão de saída                        | 103 |

| $f_{0}$                                                           | Frequência da onda de tensão de saída                                            | 103 |

| $V_{o,p}$                                                         | Valor de pico da tensão sinusoidal de saída                                      | 104 |

| $V_{C_{BL},p}$                                                    | Valor de pico da diferença de tensão entre os capacitores de bar-                |     |

| <i>.</i> .                                                        | ramento e os capacitores chaveados                                               | 104 |

| $I_{o,p}$                                                         | Valor de pico da corrente sinusoidal de saída                                    | 104 |

| $\Delta V_{C^{\mathrm{BR}},max}$                                  | Máxima ondulação de tensão nos capacitores $C_A$ e $C_B$ para ope-               |     |

|                                                                   | ração como inversor                                                              | 105 |

| $\Delta V_{C_{\mathrm{BR},max}}$                                  | Máxima ondulação de tensão nos capacitores $C_1$ e $C_2$ para opera-             |     |

|                                                                   | ção como inversor                                                                | 106 |

| $\Delta I_{L_i,max}$                                              | Máxima ondulação de corrente de entrada para operação como                       |     |

|                                                                   | inversor                                                                         | 107 |

| $\Delta I_{L_{o,max}}$                                            | Máxima ondulação de corrente de saída para operação como inversor                | 108 |

| $T_{ m o}$                                                        | Período da onda de tensão de saída                                               | 110 |

| $I_{C{ m CH,RMS}}$                                                | Corrente eficaz nos capacitores chaveados                                        | 110 |

| $I_{C{\scriptscriptstyle { m BR}},{\scriptscriptstyle { m RMS}}}$ | Corrente eficaz nos capacitores de barramento                                    | 110 |

| $I_{C_o,_{ m RMS}}$                                               | Corrente eficaz no capacitor de saída                                            | 110 |

| $I_x$                                                             | Corrente média no semicondutor $x$                                               | 111 |

| $I_{x,_{ m RMS}}$                                                 | Corrente eficaz no semicondutor $x$                                              | 111 |

| $V_{o,{\scriptscriptstyle 	ext{RMS}}}$                            | Tensão eficaz de saída                                                           | 111 |

| $I_{L_o,_{ m RMS}}$                                               | Corrente eficaz de saída                                                         | 111 |

| $I_{L_i,_{ m RMS}}$                                               | Corrente eficaz de entrada                                                       | 111 |

| $t_{\scriptscriptstyle \mathrm{AS}}$                              | Tempo de assentamento                                                            | 113 |

| %SS                                                               | Percentual de sobressinal                                                        | 113 |

| $K_v$                                                             | Ganho do sensor de tensão                                                        | 113 |

| B                                                                 | Densidade de fluxo magnético                                                     | 114 |

| J                                                                 | Densidade de corrente                                                            | 114 |

| C(s)                                 | Função de transferência do controlador                             | 116 |

|--------------------------------------|--------------------------------------------------------------------|-----|

| $v_c(s)$                             | Sinal de controle oriundo do controlador                           | 116 |

| $e_r(s)$                             | Erro de realimentação                                              | 116 |

| $r_{ef}(s)$                          | Sinal de referência                                                | 116 |

| $M_o(s)$                             | Função de transferência de pequenos sinais, do sinal de controle   |     |

|                                      | para perturbação na perturbação da razão cíclica                   | 116 |

| E(%)                                 | Erro relativo                                                      | 118 |

| $V_{\scriptscriptstyle  m TEO}$      | Valor teórico oriundo do equacionamento (cálculo do erro relativo) | 118 |

| $V_{\scriptscriptstyle 	ext{SIMUL}}$ | Valor simulado (cálculo do erro relativo)                          | 118 |

| $V_{o_{T,\mathrm{RMS}}}$             | Tensão eficaz na saída do autotransformador                        | 124 |

| $N_p:N_s$                            | Relação de transformação do autotransformador                      | 124 |

| $v_{o_T}(t)$                         | Tensão instantânea na saída do autotransformador                   | 125 |

|                                      |                                                                    |     |

# **SUMÁRIO**

| 1 INTE  | RODUÇÃO                                                      | 33         |

|---------|--------------------------------------------------------------|------------|

| 2 TOP   | OLOGIAS MULTINÍVEIS E TÉCNICA DE CAPACITOR CHAVEADO:         |            |

| UMA     | REVISÃO                                                      | 39         |

| 2.1 CA  | PACITOR CHAVEADO                                             | 39         |

| 2.1.1 P | rincípio de funcionamento de uma célula a capacitor chaveado | 39         |

| 2.1.2 A | plicações de capacitores chaveados em eletrônica de potência | 43         |

| 2.2 TO  | POLOGIAS MULTINÍVEIS                                         | 44         |

| 2.2.1 C | Conversor de ponto neutro grampeado                          | 44         |

| 2.2.1.1 | Conversor de ponto neutro ativamente grampeado               | 47         |

| 2.2.1.2 | Conversor de ponto neutro grampeado tipo T                   | 47         |

| 2.2.2 C | Conversor a capacitor flutuante                              | 49         |

| 2.3 CÉ  | LULA P2                                                      | 51         |

|         | -CC-3N OPERANDO COMO CONVERSOR CC-CC                         | 55         |

| 3.1 AN  | ÁLISE ESTÁTICA                                               | 56         |

| 3.1.1 N | lodo de operação positivo                                    | 57         |

| 3.1.1.1 | Estado topológico 11                                         | 59         |

| 3.1.1.2 | Estado topológico 01                                         | 59         |

| 3.1.1.3 | Estado topológico 10                                         | 60         |

| 3.1.1.4 | Desbalanço de tensão entre os capacitores de barramento      | 61         |

| 3.1.2 N | lodo de operação negativo                                    | <b>6</b> 1 |

| 3.1.2.1 | Estado topológico 00                                         | 62         |

| 3.1.2.2 | Estado topológico 10                                         | 63         |

| 3.1.2.3 | Estado topológico 01                                         | 63         |

| 3.1.2.4 | Desbalanço de tensão entre os capacitores de barramento      | 64         |

| 3.2 CO  | NSIDERAÇÕES FINAIS                                           | 65         |

| 4 C4Q   | -CC-5N OPERANDO COMO CONVERSOR CC-CC                         | 67         |

| 4.1 AN  | ÁLISE ESTÁTICA                                               | 68         |

| 4.1.1 P | Princípio de operação: dispositivos ideais                   | 69         |

| 4.1.1.1 | Região de operação R1                                        | 69         |

| 4.1.1.2 | Região de operação R2                                        | 71         |

| 4.1.2 E | quações de estados                                           | 72         |

| 4.1.3 E | stados topológicos – região de operação R1                   | 73         |

| 4.1.3.1 | Estado topológico 1100                                       | 73         |

| 4.1.3.2 | Estado topológico 0100                                       | 74         |

| 4.1.3.3 | Estado topológico 1101                                       | 75         |

| 4.1.3.4 | Estado topológico 1000                                       | 76         |

| 4.1.3.5 | Estado topológico 1110                                       | 76         |

| 4.1.4    | Estados topológicos – região de operação R2         |

|----------|-----------------------------------------------------|

| 4.1.4.1  | Estado topológico 0100                              |

| 4.1.4.2  | Estado topológico 0101                              |

| 4.1.4.3  | Estado topológico 1101                              |

| 4.1.4.4  | Estado topológico 1001                              |

| 4.1.4.5  | Estado topológico 1000                              |

| 4.1.4.6  | Estado topológico 1010                              |

| 4.1.4.7  | Estado topológico 1110                              |

| 4.1.4.8  | Estado topológico 0110                              |

| 4.1.5    | Equação de estado médio instantâneo                 |

| 4.1.6    | Tensão média de saída                               |

| 4.1.6.1  | Ganho estático ideal                                |

| 4.1.6.2  | Tensão média de saída não ideal                     |

| 4.1.6.3  | Tensão média de saída ideal vs não ideal            |

| 4.1.7    | Tensão média nos capacitores chaveados 8            |

| 4.1.8    | Corrente média de saída e corrente média de entrada |

| 4.1.9    | Ondulação de tensão nos capacitores chaveados 8     |

| 4.1.10   | Corrente eficaz nos capacitores chaveados           |

| 4.1.11   | Ondulação de tensão nos capacitores de barramento 8 |

| 4.1.12   | Corrente eficaz nos capacitores de barramento       |

| 4.1.13   | Ondulação de corrente no indutor de entrada 8       |

| 4.1.14   | Ondulação de corrente no indutor de saída           |

| 4.1.15   | Ondulação tensão no capacitor de saída 9            |

| 4.1.16   | Corrente eficaz no capacitor de saída               |

| 4.1.17   | Esforços nos semicondutores                         |

| 4.1.17.  | Esforços de tensão                                  |

| 4.1.17.2 | 2 Esforços de corrente                              |

| 4.2 A    | NÁLISE DINÂMICA                                     |

| 4.2.1    | Estados topológicos – região de operação R1         |

| 4.2.1.1  | Estado topológico 1100                              |

| 4.2.1.2  | Estado topológico 0100                              |

| 4.2.1.3  | Estado topológico 1101                              |

| 4.2.1.4  | Estado topológico 1000                              |

| 4.2.1.5  | Estado topológico 1110                              |

| 4.2.2    | Estados topológicos – região de operação R2         |

| 4.2.2.1  | Estado topológico 0100                              |

| 4.2.2.2  | Estado topológico 0101                              |

| 4.2.2.3  | Estado topológico 1101                              |

| 4.2.2.4  | Estado topológico 1001                              |

| 4.2.2.5 | Estado topológico 1000                                                                 | 96  |

|---------|----------------------------------------------------------------------------------------|-----|

| 4.2.2.6 | Estado topológico 1010                                                                 | 96  |

| 4.2.2.7 | Estado topológico 1110                                                                 | 96  |

| 4.2.2.8 | Estado topológico 0110                                                                 | 97  |

| 4.2.3   | Modelagem por circuito médio                                                           | 97  |

| 4.2.4   | Modelo médio linearizado                                                               | 97  |

| 4.3     | CONSIDERAÇÕES FINAIS                                                                   | 99  |

| _       | 4Q-CC-5N OPERANDO COMO INVERSOR MONOFÁSICO COM                                         |     |

|         | ARGA RESISTIVA                                                                         | 103 |

| 5.1     | ANÁLISE ESTÁTICA                                                                       | 103 |

| 5.1.1   | Máxima ondulação de tensão nos capacitores chaveados                                   | 104 |

| 5.1.2   | Máxima ondulação de tensão nos capacitores de barramento                               | 105 |

| 5.1.3   | Máxima ondulação de corrente no indutor de entrada                                     | 106 |

| 5.1.4   | Máxima ondulação de corrente no indutor de saída                                       | 107 |

| 5.1.4.1 | Máxima ondulação de corrente de saída operando com 3 níveis de                         |     |

|         | tensão de saída                                                                        | 107 |

| 5.1.4.2 | •                                                                                      |     |

|         | tensão de saída                                                                        | 108 |

| 5.1.5   | Correntes eficazes nos capacitores                                                     | 109 |

| 5.1.6   | Esforços de corrente nos semicondutores                                                | 111 |

| 5.1.7   | Tensão de saída, corrente de saída e corrente de entrada eficazes .                    | 111 |

|         | CONSIDERAÇÕES FINAIS                                                                   | 112 |

|         | MULAÇÕES E RESULTADOS EXPERIMENTAIS                                                    | 113 |

|         | EXEMPLO DE PROJETO                                                                     |     |

| 6.1.1   | Dimensionamento dos componentes de potência                                            |     |

| 6.1.2   | Projeto de controlador                                                                 |     |

|         | RESULTADOS DE SIMULAÇÕES                                                               |     |

| 6.2.1   | Conversor cc-cc operando em regime permanente e malha aberta .                         |     |

| 6.2.2   | Resposta dinâmica                                                                      |     |

| 6.2.3   | Inversor operando em regime permanente e malha aberta                                  |     |

|         | RESULTADOS EXPERIMENTAIS                                                               |     |

|         | ONCLUSÃO                                                                               |     |

|         | TRABALHOS FUTUROS                                                                      |     |

|         | RÊNCIAS                                                                                | 133 |

| APEN    | DICE A – EXEMPLO DE CÁLCULO DAS CORRENTES DOS CAPACI-                                  |     |

|         | TORES DE PROCESSAMENTO DE ENERGIA DO C4Q-CC-<br>3N ATRAVÉS DE ANÁLISE POR SUPERPOSIÇÃO | 120 |

|         | JIN AT NAVLO DE ANALIJE FUN JUFENFUJIÇAU                                               | เงฮ |

| APÊNDICE B – IGUALDADE DAS TENSÕES MÉDIAS INSTANTÂNEAS EN- |

|------------------------------------------------------------|

| TRE OS CAPACITORES DE BARRAMENTO E ENTRE OS                |

| CAPACITORES CHAVEADOS                                      |

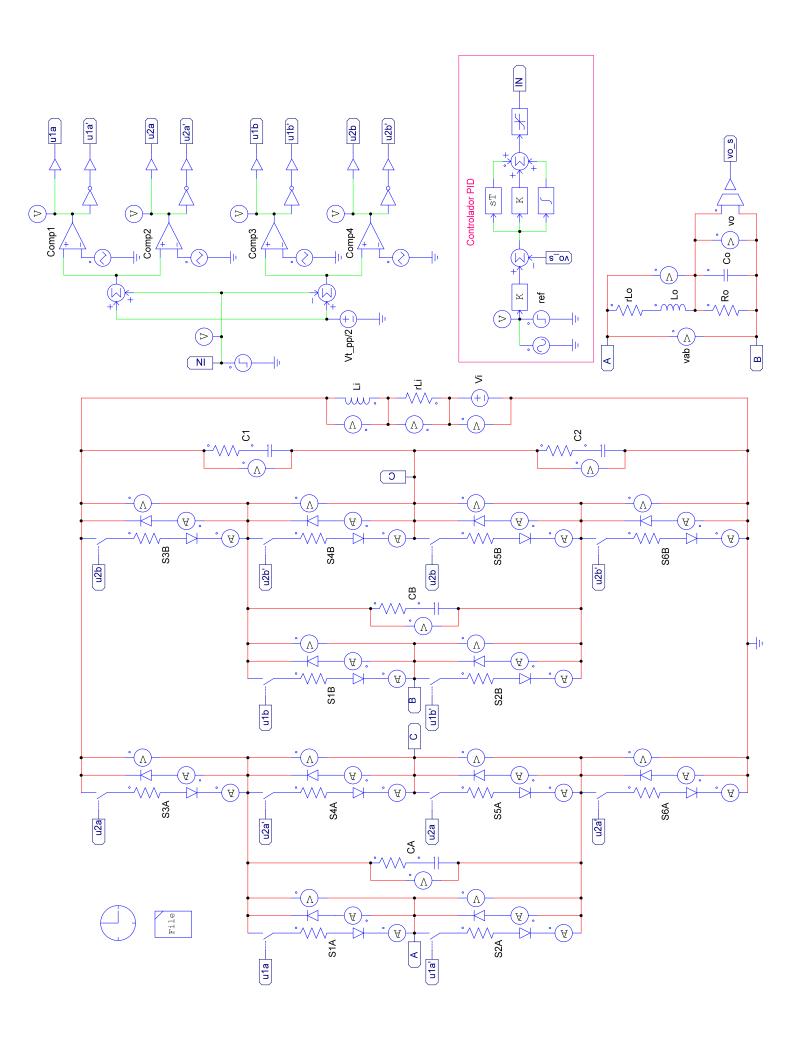

| APÊNDICE C - CIRCUITO ESQUEMÁTICO USADO NAS SIMULAÇÕES 149 |

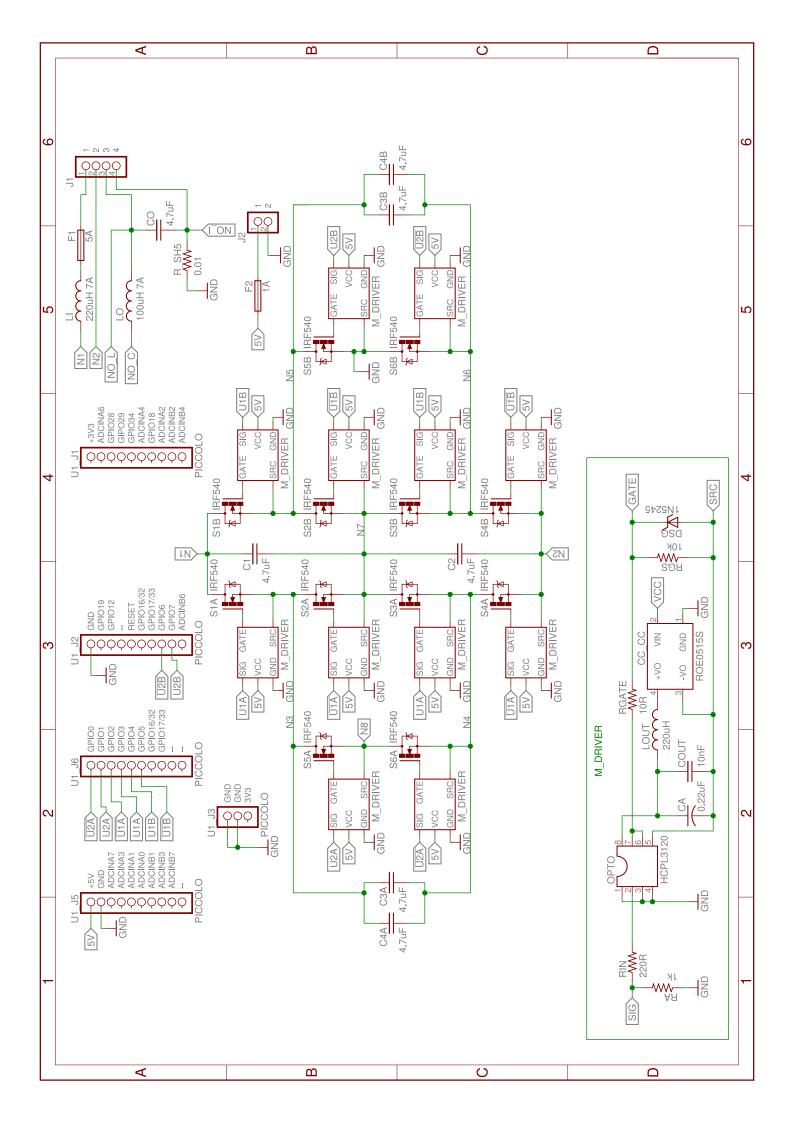

| APÊNDICE D – CIRCUITO ESQUEMÁTICO DO PROTÓTIPO 151         |

| APÊNDICE E – SOFTWARE EMBARCADO 153                        |

| APÊNDICE F - COMPARAÇÃO COM AS TOPOLOGIAS FC E NPC 167     |

|                                                            |

Capítulo 1 33

### 1 INTRODUÇÃO

Fontes de energia elétrica alternativas, como a fotovoltaica e a eólica estão ganhando espaço no cenário mundial e devem, cada vez mais, ser uma parcela significativa da produção de energia elétrica. Por exemplo, houve um superavit na produção de energia elétrica na Alemanha, em dezembro de 2017, na semana do Natal, por conta da produção oriunda de fontes eólicas e fotovoltaicas. Os preços chegaram abaixo de zero no final de semana do Natal em função do clima quente (favorecendo a produção de usinas fotovoltaicas) e dos fortes ventos na região das usinas eólicas, gerando um crédito de US\$ 60,00 por megawatt-hora aos clientes. Não sendo este um caso isolado, uma vez que em países como Bélgica, França, Reino Unido, Holanda, Suíça e na própria Alemanha já houveram eventos similares (FEITOSA JR., 2018). Contudo, a conexão destes sistemas geradores de energia elétrica à rede elétrica de distribuição ou transmissão de energia elétrica necessita de condicionamento. Conversores estáticos são utilizados para adequar os níveis de tensão e frequência de transmissão das fontes geradoras para as redes de distribuição ou transmissão.

Segundo Barbi (2005), conversores estáticos são circuitos eletrônicos responsáveis pelo controle do fluxo de potência entre 2 ou mais sistemas elétricos. Conversores estáticos são circuitos não lineares, pois usam de um conjunto de interruptores comutando em frequências relativamente altas (em relação à frequência da onda sintetizada), segundo uma sequência determinada por circuitos de comando (modulação), para gerar a forma de onda desejada na saída. Os conversores estáticos permitem o processamento de energia entre sistemas de corrente contínua (cc) e/ou corrente alternada (ca), operando em diferentes níveis de tensão, corrente ou mesmo em frequência diferentes. Os conversores estáticos são objeto de estudo da eletrônica de potência, que teve seu advento com o desenvolvimento de dispositivos semicondutores ou interruptores (tiristores, diodos, triacs MOSFETs, IGBTs, GTOs) e está em constante desenvolvimento tanto em novas tecnologias para semicondutores, quanto no desenvolvimento de novas estruturas que visam atender essas novas demandas na conversão de energia.

A abrangência de conversores estáticos, de modo geral, é limitada pelas tecnologias dos dispositivos empregados, em especial os semicondutores. A tendência, iniciada há algumas décadas, é de que os conversores estáticos passem a processar cada vez mais potência, o que esbarra nos níveis de tensão e corrente dos dispositivos empregados. Dessa forma, a potência nominal dos conversores convencionais acaba sendo limitada. Aplicações que extrapolam os limites físicos desses conversores convencionais demandam a utilização de várias unidades de processamento de energia (LEON; VAZQUEZ; FRANQUELO, 2017). Contudo, no intuito de contornar este problema, nessas últimas 5 décadas, topologias de conversores estáticos com 34 Capítulo 1

maior potência nominal, mas utilizando dispositivos limitados, vem sendo desenvolvidas na acadêmia e sendo aplicadas no meio industrial. Via de regra, essas topologias são concebidas como a junção de dispositivos semicondutores em arranjos que criam níveis intermediários de tensão, aumentado a tensão gerenciada pelo conversor e, por conseguinte, a potência. Isso é precursor dos chamados conversores multiníveis (LEON; VAZQUEZ; FRANQUELO, 2017).

Além de serem topologias que podem operar em níveis de tensão e potência mais elevados, conversores multiníveis são atrativos para aplicações que envolvem a integração de energias renováveis com os sistemas de transmissão / distribuição (usinas fotovoltaicas e eólicas), veículos elétricos (ou sistemas veiculares auxiliares em veículos de grande porte), sistemas de fornecimento ininterrupto de energia (uninterruptible power supply – UPS) *etc*.

A seguir são elencadas algumas características gerais dos conversores multiníveis que os tornam atrativos para as aplicações já citadas (LEON; VAZQUEZ; FRANQUELO, 2017):

- Grande capacidade de processamento de energia, sendo uma boa alternativa para o acionamento de motores de média tensão, bombas ou ventiladores;

- Degraus na forma de onda de saída (mais de 3 níveis), o que implica em menor distorção harmônica;

- Redução do tamanho de filtros de saída;

- Emprego de dispositivos que operam em menores níveis de tensão e/ou corrente e, por conseguinte, menores perdas por condução;

- Menores derivadas de tensão sobre a carga;

- Modularidade (em algumas topologias);

- Maior disponibilidade ou tolerância a falhas (em algumas topologias).

Contudo, apresentam maior complexidade nas técnicas de controle e modulação, maiores níveis de isolação de tensão do barramento e necessidade de balanço de tensão(LEON; VAZQUEZ; FRANQUELO, 2017).

De forma geral, conversores multiníveis são empregados em sistemas que demandam grande processamento de energia. Contudo, estudos de topologias multiníveis em aplicações de baixa tensão e baixa potência vem sendo realizados nos últimos anos. Dentre esses estudos cita-se sistemas de geração de energia fotovoltaica (ESFANDIARI; BAHRAMINEJAD, 2014); carregadores de bateria (PENG; ZHANG; QIAN, 2002); e acionamento de motores e máquinas síncronas (MECKE, 2011). Nesse tipo de aplicação o uso de conversores multiníveis justifica-se pela maior qualidade de energia e menor índice de distorção harmônica (Total Harmonic Distortion – THD).

Capítulo 1 35

Kouro et al. (2010) apresenta alguns desafios relacionados às topologias multiníveis e as respectivas técnicas de modulação, principalmente em relação às soluções comerciais. Alguns pontos discutidos por Kouro et al. (2010) permanecem atuais, mesmo quase uma década depois. Soluções comerciais de conversores multiníveis de alta potência empregam IGBTs como interruptores e operam com frequências de chaveamento inferiores a 1 kHz, visando melhorar a eficiência, levando os dispositivos ao limite; e procurando viabilizar a construção de sistemas de arrefecimentos (tornando-os factíveis). Contudo, operar em baixas frequências de chaveamento introduz harmônicas de menor ordem e manter alta performance nesse cenário mostra-se um desafio, embora conversores de baixa potência possam operar com frequências de chaveamento em algumas dezenas de kilo-hertz sem maiores problemas. Outro problema inerente às topologias multiníveis são as perdas por condução, que são mais representativas – quando comparadas às estruturas de 2 níveis de tensão – em função do número de componentes em série – para sintetização dos múltiplos níveis de tensão – em determinados estados de chaveamento. Ademais, em geral existe a possibilidade de algum interruptor (ou diodo) ser submetido, instantaneamente, a uma tensão superior a idealmente prevista. Isso está relacionado a entrada e saída de condução, tempo morto e defasagem de sinais de comando dos interruptores. Em função disso normalmente empregam-se interruptores (ou diodos) com tensões de bloqueio muito superiores as idealmente necessárias, e.g. conversores de 3 níveis de tensão utilizam interruptores que suportam à tensão de barramento, enquanto que idealmente só precisariam suportar metade da tensão de barramento.

A contribuição deste trabalho consiste na proposta e estudo de um conversor multinível composto por um par de células P2 de 3 níveis de tensão (PENG, 2001), onde cada célula constitui uma perna de uma estrutura monofásica que opera nos 4 quadrantes, isto é, tensão positiva / negativa e corrente positiva / negativa, no qual emprega-se uma técnica de capacitor chaveado. O conversor é abaixador de tensão e pode sintetizar até 5 níveis de tensão de saída. As células são constituídas por 3 capacitores que processam energia através da comutação de 6 interruptores e compartilham um par de capacitores, de modo que a topologia seja constituída por 4 capacitores de processamento de energia, 2 deles associados na forma de um divisor capacitivo (compartilhados), junto ao barramento de entrada, e 2 capacitores chaveados; e 12 interruptores.

Figuram entre as possíveis aplicações para o conversor proposto: carregamento de baterias em veículos, a exemplo da aplicação proposta por Peng, Zhang e Qian (2002) ou em microrredes de energia *off-grid*, operando como conversor cc-cc bidirecional em corrente; acionamento de motores de corrente contínua, operando como conversor cc-cc nos 4 quadrantes; e como inversor em microrredes de energia *on-grid*. Aplicações nas quais justifica-se o uso de um conversor multinível para se alcançar

36 Capítulo 1

maior qualidade de energia e menor THD ou aplicações em que o menor peso (não há componentes magnéticos no estágio de processamento de energia) ou maior densidade de potência são relevantes.

Além da topologia proposta, é estudada a variante topológica constituída por uma única célula P2 de 3 níveis de tensão. Dessa forma discriminou-se como Conversor de 4 de Quadrantes a Capacitor Chaveado com 5 Níveis de tensão de saída (C4Q-CC-5N) a variante topológica que é constituída por duas células P2 e como Conversor de 4 de Quadrantes a Capacitor Chaveado com 3 Níveis de tensão de saída (C4Q-CC-3N) a variante constituída por uma única célula. O estudo de ambas as topologias considera o uso de filtros de entrada e de saída. O estudo do C4Q-CC-3N se fez necessário para justificar a escolha do C4Q-CC-5N como tema desta dissertação, uma vez que o C4Q-CC-5N apresenta maior viabilidade técnica, embora demande de um número maior de componentes de potência.

O C4Q-CC-5N apresenta o auto-balanceamento das tensões dos capacitores de processamento de energia, sendo desnecessário o uso de técnicas específicas para o controle de tensão, o que é um desafio para muitas das topologias multiníveis. Para tanto, diferentemente de outras topologias multiníveis abordadas na revisão bibliográfica deste trabalho, nas duas variantes topológicas apresentadas os capacitores de processamento de energia não são colocados em flutuação em nenhum dos estágios topológicos, caraterizando a técnica de capacitor chaveado (ZAMIRI et al., 2016; BABAEI; GOWGANI, 2014; QIAN et al., 2012). Empregou-se a técnica de capacitor chaveado em função da hipótese de que estados topológicos onde os capacitores de processamento de energia estariam em flutuação tornariam a estrutura suscetível a desbalanços de tensão. Ambas as variantes são estudadas no modo de operação como conversor cc-cc (de corrente contínua para corrente contínua), mas visando demonstrar que o C4Q-CC-5N promove o auto-balanceamento das tensões dos capacitores, também é apresentado o estudo dessa variante topológica como inversor de tensão ou conversor cc-ca (de corrente contínua para corrente alternada), uma vez que operando como inversor de tensão o conversor é excitado nos 4 quadrantes.

O objetivo principal desse trabalho é demonstrar matematicamente que a topologia apresenta o auto-balanceamento das tensões dos capacitores de processamento de energia através do equacionamento das tensões sobre esses capacitores para operação como conversor cc-cc em condições de regime permanente; o que é uma vantagem frente a outras topologias multiníveis que utilizam de capacitores de processamento de potência e necessitam de estratégias específicas relativamente complexas para o controle do desbalanço de tensão nos capacitores. Como objetivo secundário propõe-se desenvolver uma metodologia que permita o projeto preliminar do conversor. Para tanto, são considerados os seguintes objetivos específicos:

Analisar as etapas de comutação do conversor;

- Modelar o conversor em espaço de estados;

- Equacionar as ondulações de tensão e corrente nos componentes passivos;

- Equacionar os esforços de corrente e tensão nos componentes passivos e semicondutores;

- Obter o modelo dinâmico de pequenos sinais do conversor;

- Expandir o equacionamento para operação como conversor cc-cc para a operação como inversor de tensão;

- Validar o princípio de funcionamento apresentado e a hipótese de autobalanceamento das tensões dos capacitores de processamento de energia experimentalmente.

Este trabalho está organizado em 7 capítulos. No Capítulo 2 é feita a revisão bibliográfica e do estado da arte a cerca das principais topologias multiníveis. No Capítulo 3 é apresentada a análise estática do C4Q-CC-3N . Nesse capítulo são equacionadas as tensões nos capacitores e é demonstrado que para essa variante há grandes restrições quanto a faixa de operação do conversor. No Capítulo 4 são apresentadas a análise estática e dinâmica do C4Q-CC-5N. Nesse capítulo são obtidos os valores médios das correntes de entrada e saída e das tensões nos capacitores; as ondulações de tensão e corrente nos componentes passivos; os esforços de corrente nos semicondutores; e o modelo dinâmico de pequenos sinais do conversor. Nesse capítulo também é discutida a questão do auto-balanceamento das tensões dos capacitores de processamento de energia. No Capítulo 5 o equacionamento desenvolvido no Capítulo 4 é adaptado para operação como inversor de tensão. No Capítulo 6 é apresentado um exemplo de projeto utilizando o equacionamento desenvolvido no Capítulo 4. As grandezas obtidas no exemplo de projeto são utilizadas em simulações, tanto para operação como conversor cc-cc como para inversor de tensão. Os resultados de simulação são comparados, quantitativamente, aos valores previstos através das equações desenvolvidas nos Capítulos 4 e 5. Ainda no Capítulo 6 são apresentados resultados experimentais obtidos através de um protótipo de 115 W, com o intuito de validar o princípio de funcionamento do conversor. No Capítulo 7 são apresentadas as conclusões gerais do trabalho e algumas propostas para continuidade deste trabalho.

No decorrer do mestrado foram elaborados 2 artigos científicos, um artigo em conferência e outro em periódico. O artigo apresentado em conferência (TOMIN JR.; LARICO; GREFF, 2018) aborda o tema desta dissertação, no entanto ainda em uma fase inicial, em que muito do que foi desenvolvido e concluído nesta dissertação não é apresentado. O artigo a ser publicado em periódico (LARICO; TOMIN JR.; LARICO,

2020), embora não aborde o tema deste trabalho contribuiu para o aprendizado do autor quanto as técnicas que foram empregadas na análise deste conversor de 4 quadrantes a capacitor chaveado.

# 2 TOPOLOGIAS MULTINÍVEIS E TÉCNICA DE CAPACITOR CHAVEADO: UMA REVISÃO

Neste capítulo é apresentado e discutido o estado da arte das principais topologias multiníveis e da técnica de capacitor chaveado. A topologia proposta é composta por duas células P2 (PENG, 2001) de 3 níveis de tensão, arranjadas como pernas de um único conversor, na qual é aplicada a técnica de capacitor chaveado. Por se tratar de uma topologia multinível em tensão que utilizada da técnica de capacitor chaveado, a discussão limita-se às topologias multiníveis em tensão e ao princípio de funcionamento de uma célula a capacitor chaveado, com breve menção às topologias que utilizam dessa técnica.

#### 2.1 CAPACITOR CHAVEADO

Os conversores a capacitor chaveado (switched capacitor converter – SCC) em geral são pequenos, leves, com alta eficiência e alta densidade de potência. Esses conversores apresentam grande densidade de potência, em torno de 1,4 kW/L, característica atrativa para aplicações típicas de eletrônica de potência (IOINOVICI, 2001).

A técnica de capacitor chaveado é aplicada em diferentes níveis de potência. Na faixa dos miliwatts estruturas a capacitor chaveado são utilizadas como fonte de alimentação para blocos funcionais como memórias E²PROM e Flash (LIN; CHUA, 1977; DICKSON, 1976). Para o nível de potência de vários watts os SCCs podem fornecer vários níveis de tensão e corrente contínua em sistema de processamento de energia. Tais aplicações incluem fontes de telefones celulares, *tablets* e computadores portáteis (WONG; MAK; IOINOVICI, 1993; MAK; WONG; IOINOVICI, 1995). Para níveis de potência mais altos, de centenas de watts até dezenas de kilowatts os SCCs são empregáveis em sistemas automotivos, em veículos elétricos (PENG; ZHANG, 2002; LI et al., 2017), em sistemas de geração de energia renovável ou em conversores de uso geral (LI et al., 2017; VECCHIA; LAZZARIN; BARBI, 2015; DIAS; LAZZARIN, 2016).

A seguir é apresentado o princípio de funcionamento de uma célula a capacitor chaveado e na sequência é contextualizado o uso da técnica de capacitor chaveado na eletrônica de potência.

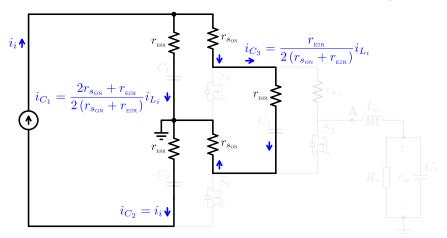

# 2.1.1 Princípio de funcionamento de uma célula a capacitor chaveado

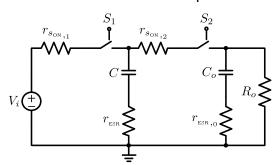

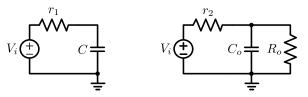

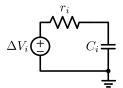

Um circuito básico a capacitor chaveado, apresentado por Ben-Yaakov (2012), é mostrado na Fig. 2.1. Nessa figura são representadas as resistências de condução dos interruptores  $r_{\scriptscriptstyle SON}$  e as resistência série-equivalente dos capacitores  $r_{\scriptscriptstyle ESR}$ . Conversores a capacitor chaveado são circuitos compostos unicamente por interruptores e capacito-

res no estágio de processamento de energia, isto é, não há elementos indutivos nesse estágio.

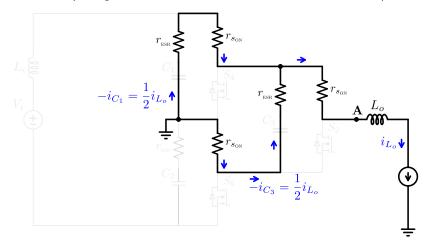

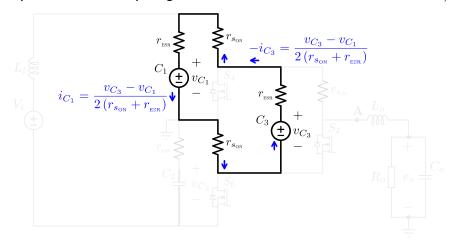

Figura 2.1 – Célula básica de capacitor chaveado

As etapas de operação de uma célula a capacitor chaveado resume-se a duas: carga, quando o capacitor armazena energia, corresponde ao estado em que o interruptor  $S_1$  está conduzindo e  $S_2$  está aberto (ver Fig. 2.1), como pode ser visto na Fig. 2.2(a); e descarga, quando o capacitor fornece energia à carga, corresponde ao estado em que o interruptor  $S_2$  está conduzindo e  $S_1$  está aberto (ver Fig. 2.1), como pode ser visto na Fig. 2.2(b).

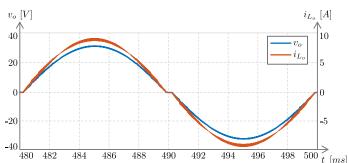

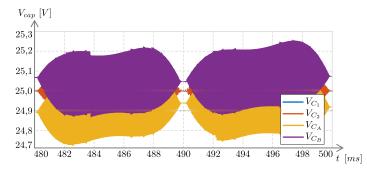

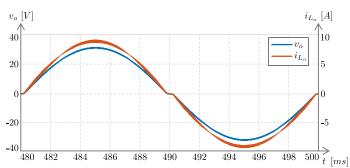

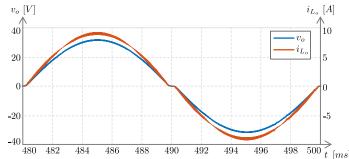

Figura 2.2 - Sub-circuitos equivalentes do SCC da Fig. 2.1